Many rumors about AMD's Bulldozer performance in multi-threaded tasks have lately reached the Web, thanks to the modular approach used by the company when designing its next-generation high-performance architecture.

Now, however, we have finally received a response from AMD as one of its senior officials has detailed the way in which throughput scales when extra modules are added.

This information was provided by John Fruehe, director of Product Marketing for Server, Embedded and FireStream products at AMD, in a post on the XtremeSystems forum.

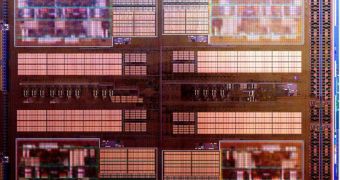

Bulldozer is AMD's next-generation high-performance CPU architecture that was designed from the ground up in order to eliminate some of the redundancies that come with traditional multi-core chips.

As a result, the processor uses a modular construction, each module being comprised of two 128-bit FMA floating point units, which can be combined into one 256-bit FPU, two integer cores, with four pipelines each, and as much as 2048KB of L2 cache.

Thanks to this design approach many have speculated that a Bulldozer module will face a certain performance hit, when both cores are fully loaded, compared to native dual core CPU.

However, as AMD's official explains, the penalty won't be as severe as previously thought, since adding a second core to a module only decreases the throughput of the whole module by 7-8% when compared to a dual core chip (based on the same architecture).

Compared to Intel's Hyper-Threading technology, which records a 39.5% hit when both cores are fully loaded, AMD's approach delivers far better throughput per core.

In addition, by making the architecture modular and by sharing some resources, AMD was able to squeeze more throughput out of the design than if it used independent cores or tried to use HyperThreading.

Advanced Micro Devices will showcase Bulldozer at the CeBIT 2011 fair, and the official launch is expected to take place in Q2 2011.

14 DAY TRIAL //

14 DAY TRIAL //