Microprocessors on the market today come with a varied number of processing cores, ranging from 1 to 12. But manufacturers that want to produce 24-core or 48-core chips cannot be sure that their designs would work when completed. This is why researchers have created a simulation for these devices.

Scientists at the Massachusetts Institute of Technology (MIT) Department of Electrical Engineering and Computer Science (EECS) announce the development of Hornet, a modeling tool capable of discovering flaws in new, multi-core processor architectures.

While large companies are very interested in moving multi-core technologies forward, they are also wary of the amounts of money they would lose if they invested millions of dollars into a faulty chip. Some of the issues that may affect these devices cannot even be imagined at this point.

Hornet was developed with the express purpose of allowing engineers to test their new architectures before they commission them to be built. Investors are afraid of catastrophic problems that may occur from processes that have no bearing on overall performances in a 4- or 8-core processor.

What hornet does is it models the performance of multi-core chips much more accurately than its predecessors, thus allowing engineers to quantify the chances they have of getting things done properly the first time, and avoid losing money.

Details of how the simulation works were first presented at the Fifth International Symposium on Networks-on-Chip, in 2011. A new version of the tool will be published in an upcoming issue of the journal IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems.

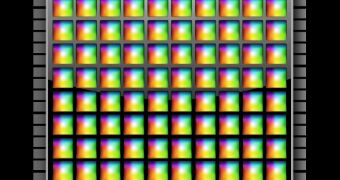

Improvements include the ability to take into account factors such as power consumption, inter-core communication capabilities, the time required to process individual tasks in each core, as well as the efficiency and timing of memory access.

Hornet was not developed to replace other simulation techniques, but rather to work side-by-side with them. A widely-used tool is a series of computer software that simulated the complex flow of data through a multi-core processor. The other is a programmable chip that can be made to replicate the behavior of more advanced processors.

“We think that Hornet sits in the sweet spot between them,” says MIT EECS PhD student Myong Hyon Cho, one of Hornet's developers.

14 DAY TRIAL //

14 DAY TRIAL //