Rambus has proudly unveiled its Mobile XDR architecture, which promises to yield mobile memory with a higher bandwidth at a lower power consumption. The technology is based on the innovations brought about by the Mobile Memory Initiative introduced last year. This architecture will supposedly enable a memory bandwidth of 4.3Gbps per pin, which means that SoC platforms can achieve a bandwidth of more than 17GB/s from a single Mobile XDR DRAM device, even while the battery life is extended by more than 30 minutes.

Among the innovations incorporated in the Mobile XDR technology are the FlexClocking Architecture, the Advanced Power State Management (APSM) and VLSD (Very Low-Swing Differential Signaling). The FlexClocking simplifies the design of the DRAM interface through asymmetric partitioning and through placing critical calibration and timing circuitry in the SoC interface.

VLSD is a ground-referenced, bi-directional, differential signaling technology that offers a cost-effective, low-power but high-performance solution for applications in need of extra bandwidth at a lower power. Finally, the APSM reduces the memory system power and enables ultra-fast transition times between various low-power and operating modes.

“Future mobile applications demand far higher performance and longer battery life than today’s mobile products can achieve,” Sharon Holt, senior vice president of Licensing and Marketing at Rambus, said. “Mobile XDR memory provides the ideal solution for designers to offer leading-edge mobile content in a dramatically lower power and cost-effective manner. Uniquely, the Mobile XDR architecture delivers these benefits in SoC and DRAM devices that can be built with current manufacturing infrastructure reducing both risk and time-to-market.”

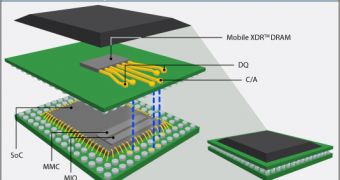

The Mobile XDR, with Mobile XDR DRAM, Mobile XDR memory controller PHY (MIO), and the Mobile XDR as key components, will enable system designers to reduce the memory subsystem power. This will increase the battery life across applications such as stereoscopic 3D or voice transmission. The architecture also integrates the Rambus FlexPhase and Microthreading technologies, for a further boost in power efficiency.

More information on the Rambus Mobile Memory Initiative may be found here.

14 DAY TRIAL //

14 DAY TRIAL //