Since there has been a lot of talk about semiconductor manufacturing facilities preparing tools and fabs for the 45nm manufacturing process, we supposed that Intel would have to comment something on this case, and as information about the 45nm process node had become generally available and continuously increasing in quantity, they came forth with some confessions of their own.

According to their decision of releasing a new type of product every two years, a decision strongly related to their attempt to keep up with Moore's Law, the company is going to launch an entirely new processor microarchitecture called Penryn in the second half of 2007. These processors are built on the 45nm Hi-k process gate with hafnium-based high-K + metal gate transistor design. They have mentioned a number of 15 45nm Hi-k product designs in development, which include dual and quad-core processors for the desktop segment, dual core mobile processors and dual and quad-core offerings for the server segment.

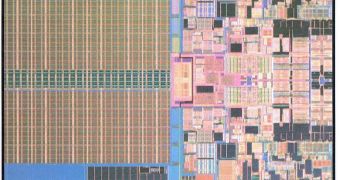

Two 45nm fabs will be completed by the end of the year with another two by the end of 2008. These will help deliver Intel's next generation processors, which, in their quad-core version will have 820 million transistors. The dual core versions, thanks to the Hi-k manufacturing process, will have a reduced die size by 25% from Intel's current 65nm products; it will be 107mm2 in size, compared to 143mm2.

On the mobile Penryn processors, Intel has added a new advanced power management state, C6, also called Deep Power Down Technology, which completely shuts down the core and turns off all of the caches, thus increasing the battery life on notebooks through low levels of power consumption. Along side this Intel has also enhanced the Dynamic Acceleration Technology, which effectively transfers the power freed up by shutting down one core to the active one, it may be thought of as an opposite to Enhanced Intel SpeedStep Technology. By monitoring the load of the processor it is overclocking it on the fly, working with single threaded or multi-threaded applications that do not require a secondary thread or core, it reduces the power on one core, and increases the active one dynamically.

Another surprise they have in store is the introduction of an actual Streaming Single Instruction Multiple Data Extensions 4 (SSE4), unlike the SSSE4 instruction currently available on the 65nm products. This is a part of Intel's Super Shuffle Engine, a ?full-width, single-pass shuffle unit that is 128-bits wide, Penryn processors can perform full-width shuffles in a single cycle?, thus improving the performance of SSE2, SSE3 and SSE4 instructions. Data computations are going to be realized twice as fast than previous generations of processors through a new faster divide technique called Radix 16, which divides instructions and commands for increased computer performance.

The Penryn processors are slated to have up to 6MB L2 cache in their dual core offerings and up to 12MB L2 cache for the quad-core versions. On the other side, Intel has mentioned that following Penryn, the 32nm process node Nehalem architecture will come as a replacement to Penryn and it will bring a lot of goodies along. Nehalem will be similar to AMD's Barcelona processors in many ways; first, they say it will have the same type of cache architecture; L1 and L2 independent caches per each core, and shared L3 cache, an integrated memory controller (IMC), a change from current bus architecture to a Common Serial Bus (CSI) a number of serial interconnects similar to HyperTransport and PCI Express.

It is also highly possible that Intel's ?high performance integrated graphics engine? will be somewhat similar to AMD's Fusion initiative, being able to create cheap and versatile solutions for the mainstream and entry-level markets, with a choice of usage even on the mobile segment. Other important features will be the introduction of the Simultaneous Multi-Threading (SMT) technology, which is said to be similar to Hyper-Threading, and also an option of scalable computer cores and cache sizes, ranging from 1 to more than 8 cores and, through SMT, 1 to more than 16 threads.

The production for Nehalem processors using the Hi-k 45nm process node will begin in 2008 with availability in the second half of the same year, and full production in 2009. Following the 45nm Nehalem architecture, Intel has Westmere, a derivative of Nehalem slated for production on the 32nm process node, while Gesher will overtake this latest architecture as a completely new concept, and all of this will take place in a time frame spanning on four years. Get ready, set, go!

14 DAY TRIAL //

14 DAY TRIAL //