If you have been keeping up to date with the latest developments in the processors world then you surely know that just a few months ago Intel sampled a massively parallel 48-core chip to academic institutions, the chip giant now stating that using the same architecture, the company is able to built a processors with up to 1,000 cores.

According to Intel, building such a chip is no easy feat, since hitting about 1,000 cores means the diameter of the mesh, grows so much that it stuffs up performance, since current CPU architectures depend of cache coherency for using the system's memory.

As a result, the protocol overhead quickly grows with the number of cores, a 'coherency wall' being hit at a certain point, meaning that overhead will exceed the performance increase brought by adding cores.

In order to get past this wall, Timothy Mattson, the engineer presenting the 1,000 core processor project at the Supercomputing 2010 conference, says that cache coherency must be removed all together in a similar way to that used in the 48-node chip sampled to academic institutions this spring.

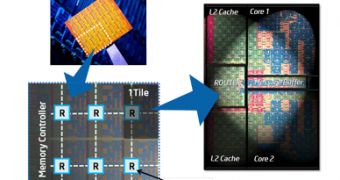

Although this chip used a pretty basic architecture when it came down to its x86 cores (that was similar to that of an 1994 Pentium processor), each core did feature an advanced "mesh interface component" that split data into packages in order to communicate with an on-board router.

As a result, this allowed for the installation of a TCP/IP protocol on the data link layer, each node being able to run a separate Linux-based OS.

Furthermore, Intel scientists also developed a small API library for passing messages along the cores, dubbed RCCE, that proved to be as speedy as the TCP/IP protocol.

However impressive all this may sound, one has to keep in mind that, although possible, we are still far off from seeing such a chip being developed, especially considering that Intel hasn't made any promises in this regard. (via TechEye)

14 DAY TRIAL //

14 DAY TRIAL //