Existing DDR3 memory can operate at 11 GB/s, which is actually not too shabby, but the time may soon come when that specification is considered scoff-worthy, and it will all be the HMC Consortium's fault.

The Hybrid Memory Cube Consortium was very thorough and meticulous in its development of the HMC standard.

Some may even say it took more than its share of time putting together and refining the spec.

Then again, when introducing such a radical new approach to random access memory, special care is definitely warranted.

In any case, the 17-month-long efforts have finally culminated in the HMC Specification 1.0, which lets companies build 2 GB, 4 GB and 8 GB RAM chips.

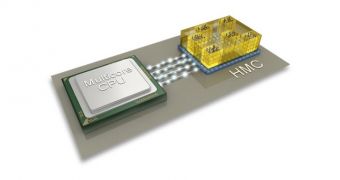

The reason for these capacities is the stacked approach, where chips are placed on top of one another. HMC has a high power efficiency and much better speed because of this.

The first products won't achieve the full potential of course, but there is definitely a lot to look forward to.

After all, it's not every day that a RAM platform provides the prospects of a bandwidth of 320 gigabyte per second (GB/s).

In 2014, the first products will arrive, with data link speeds of 15 Gbps to 28 Gbps.

"This milestone marks the tearing down of the memory wall," said Robert Feurle, Micron's vice president for DRAM marketing.

"The industry agreement is going to help drive the fastest possible adoption of HMC technology, resulting in what we believe will be radical improvements to computing systems and, ultimately, consumer applications."

It will be interesting to see how HMC faces off with DDR4. While the former is "a revolutionary technology that is a complete paradigm shift from current memory architectures," the latter is a new "an evolutionary standard." Perhaps HMC will be able to incorporate DDR4 chips at some point.

14 DAY TRIAL //

14 DAY TRIAL //