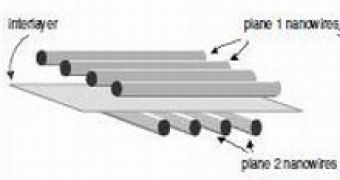

HP has released some interesting details about a "hybrid" nano-CMOS chips that could result in much smaller chip structures and extend the physical limits of Moore's law. At the same time, the integration of the Crossbar could also result in a constant decrease of the power consumption. If the crossbar technology will be applied, it could lead to a new type of field programmable gate arrays (FPGAs) that are said to be about eight times denser that today's devices. The technology's base will be represented by a crossbar switch structure, called "field programmable nanowire interconnect (FPNI)," that is placed on top of the CMOS gate.

"As conventional chip electronics continue to shrink, Moore's Law is on a collision course with the laws of physics. Excessive heating and defective device operation arise at the nanoscale. What we've been able to do is combine conventional CMOS technology with nanoscale switching devices in a hybrid circuit to increase effective transistor density, reduce power dissipation, and dramatically improve tolerance to defective devices, " said Stan Williams, an HP senior fellow at the Quantum Science Research division of HP Labs.

HP claims that the signal routing inside a chip could be controlled by the crossbar and by that it could lead to a significant decrease in the power consumption. "Since conventional FPGAs use 80 to 90 percent of their CMOS for signal routing, the FPNI circuit is much more efficient," said HP.

As a first practical result of this technology, a 15 nm crossbar and 45 nm CMOS could come out in 2010. A 4.5 nm crossbar shrink could be possible by 2020, extending Moore's law even further into the future. A 4.5 nm crossbar with 45 nm CMOS is said to have only about 4% of effective surface when compared to the classic 45-nm CMOS FPGA and that could lead to multi-CPU servers consuming roughly the same as today's home PCs. On the downside, a hybrid device will have a higher defect rate when compared to a classic CMOS chip due to the small nanowires and crossbar but if we're to push actual CPUs even further, there's no other way.

14 DAY TRIAL //

14 DAY TRIAL //