The University of Glasgow has been elected to join Semiconductor Research in setting the basis of the next 8-nanometer architecture. The University will have to take care of identifying the best p-channel material to scale the MOSFET minimum feature size - including gate length - to match the new architecture.

The institution has made progress in researching on compound semiconductor materials, and they are alleged to find a fast end efficient solution of miniaturizing silicone chips in a four to six years interval. This interaction between the University and Semiconductor Research is a three-year partnership program that is supposed to boost the global research, in the industry, for achieving n- and p-type channels on compound semiconductors. The project is due to start on January 1st 2008 and is worth a total investment of $2.5 million.

"Being able to utilize MOSFETs in compound semiconductors has been the elusive Holy Grail of scaling for 30 years. With what we expect to accomplish with the University of Glasgow, we may be only 2-3 years away from achieving that breakthrough", said Jim Hutchby, senior scientist for the Global Research Collaboration (GRC), a unit of the SRC that takes care of narrowing the options for pushing CMOS to its ultimate limit.

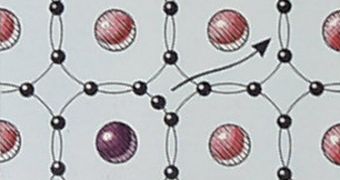

Implementation of compound semiconductor materials, such as indium gallium arsenide or other elements to replace silicon, is essential for boosting silicon switching speeds. The second objective targets carrier velocities, and researchers in the Glasgow University have to strain p-type compound semiconductors following the silicon models.

"When the day comes that Moore's Law scaling of classical silicon CMOS slows, the benefits from our extending the silicon chip using compound semiconductors could be profound for the electronics industry. At that point, we'll have developed with compound semiconductors a new set of materials and devices to improve both the power dissipation and speed of the historically successful CMOS technology."

14 DAY TRIAL //

14 DAY TRIAL //