Both Intel and AMD, the majors players in the processor industry, have introduced their latest chips (we're talking Shanghai and Core i7) with great fanfare, and people have jumped at the chance of testing their capabilities right away. The chips have been designed for use in two different areas of the market, yet the guys from AnandTech thought it would be interesting to have them subjected to the same test. Somehow, it proved they were right in doing so.

According to the piece written after tests were complete, they took a closer look at the performance capabilities of the 45 nm Opterons, Xeons and Core i7 CPUs. The benchmark that returned the most interesting performance results was LINPACK. The guys used for test a matrix size of 18000, which needed 2.5 GB of RAM, as they had only 3 GB of DDR-3 on the Core i7 platform. Also, they used the 9.1 version of Intel's LINPACK to have the same binary on both platforms. According to them, the current 10.1 version does not work on AMD CPUs.

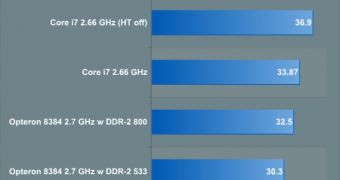

The comparison between the two parts may not be considered the fairest one, as the Nehalem platform uses unbuffered RAM that comes with a lower latency and higher bandwidth than what the future Xeon “Nehalem” will sport. Even so, a general picture of how the new Shanghai would compare to Intel's architecture was drawn, and the screenshot attached to this article speaks for itself.

The Hyperthreading (SMT) offers a great advantage to the Nehalem CPU when multi-threaded applications are involved, yet LINPACK slows the CPU by 10 percent. Although this might be an application able to slow down Intel's technology, there are many other HPC benchmarks that show larger gaps. For what it’s worth, Shanghai has the chip already on the market, while Nehalem-based Xeons will only arrive a few months from now.

The memory subsystem has only a small impact on performance, translated into a 6 percent gain, while the memory speed is increased by 50 percent. The effect of the memory speed is minimized due to the optimizations of the Math Kernel Libraries. For comparison, the triple channel DDR-3 memory system of Nehalem proves more than worthy on other HPC applications, says AnandTech.

14 DAY TRIAL //

14 DAY TRIAL //