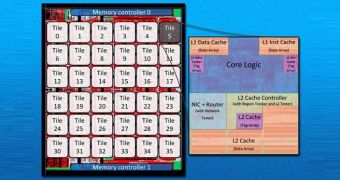

This week the International Symposium of Computer Architecture is under way, and during the event a team lead by the Singapore Research Professor of Electrical Engineering and Computer Science at MIT, Li-Shiuan Peh, has unveiled an experimental 36-core chip design called a “network on chip” or NoC.

The chip, which has been dubbed "Scorpio" bundles a system that allows the reduction of the number of cycles needed to execute tasks on a computer by allowing data transfers between cores and cache to happen more fluidly.

As CPU cores numbers increase, those currently designing a computer chip have to find a way to allow cores to communicate more efficiently.

Peh has argued for years that future chips will need to act like mini Internets, a concept that translates into each core having an associated router with data transfer between cores in packets.

According to MIT, the most common method of communication between cores is the bus. Nevertheless, this system is quite limited as it can only scale to about 8 or 10 cores before being plagued by latency or running out of power.

The NoC will ditch the bus and take up short interconnects set up between adjacent cores. As mentioned above, each core takes advantage of its own router and is able to move a packet of request across the chip, in a manner that resembles what’s being used by Internet Protocol.

“You can reach your neighbors really quick. You can also have multiple paths to your destination. So if you’re going way across, rather than having one congested path, you could have multiple ones,” explains one of the MIT team members.

However, the bus does have its advantages. When it comes to cache (local, high-speed memory bank in which frequently used data gets stored) bus is able to maintain improved cache coherence.

But the team solves the problem on NoC by bundling the chip with a “shadow network” used so the cache in a core is able to anticipate data packets.

When a data pack arrives, it will be broken down and moved across multiple closers and into their own cache, capable of temporary hosting data.

The network allows an existing cache coherency protocol called “snoppy” to function optimally on NoCs.

Under the influence of the shadow, the MIT team found performance improvements of 24.1% and 12.9% in 36 and 64-core stimulation compared to chips that did not take advantage of the network.

The chip is made using the 45-nanometer process, with core parts being made available by Freescale Semiconductor.

However, note that Scorpio is a prototype which is currently used mostly for research activities, so it’s pretty unlikely that it will make it on the market one day.

14 DAY TRIAL //

14 DAY TRIAL //