INTEL is said to release a study that concerns the Floating Body Cell memory, a new kind of embedded memory with a lot of potential if it will become wide available. The Floating Body Cell Memory uses only one transistor per cell so that makes it slower when compared to SRAM, but easier to manufacture than DRAM cells.

As a reminder, SRAM has 6 transistors per cell and that makes it really big, but it is also fast and easy to manufacture. eDRAM cells have a transistor and capacitor making them more dense than SRAM but that also translates into slower modules than their SRAM counterparts. Even more, the eDRAM cells are more difficult to manufacture and the process takes more time.

Berkeley and Toshiba have done a lot to develop working models for the FBC. Berkeley started it out and Toshiba seems to have pushed further into the modern era. While Berkeley's model was simpler, Toshiba changed the substrate voltage and the thickness making the cells easier to manufacture. Because FBC uses a "history" effect (similar to a capacitor) the trigger is directly correlated to the thickness and the voltage that is being applied.

Although things seem pretty simple, the tuning of the voltage and the thickness requires a lot of time, since wrong parameters can affect the logic of the transistor. And that can result in corrupted data along with several other problems. Here's the part where INTEL's design adds something to the original FBCs.

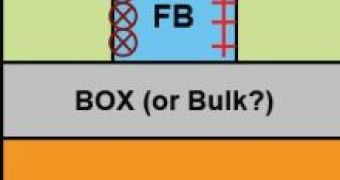

Instead of tuning the voltage and the cross section, INTEL decided to decouple the tunable parts of the FBC. They put a Front Gate (FG) and Back Gate (BG) on either side of the FBC instead of implementing these sections below and above the cell. The advantage of this method is that the tuning does not seem to affect the logic of the transistor especially when using 65nm process or smaller. What remains to be seen is whether they can mass produce FBC based memory modules.

14 DAY TRIAL //

14 DAY TRIAL //