Armonk, New York-based IBM has recently unveiled details on its much-anticipated Power7 chip for high-performance server systems, which is expected to power upcoming high-end machines. Details on the new processor have been revealed at the Hot Chips 09 Symposium in Sheraton, Palo Alto, by the company's William Starke, who said that it had been designed to deliver an 8-core chip architecture with 1.2B transistors and a performance level of 20,000 coherent operations in flight.

According to the available details, the new Power7 processor will boast 12 execution units per core, with 32 threads per chip and advanced pre-fetching data and instruction sets. “Power7 is an 8-core, high performance server chip. A solid chip is a good start. But to win the race, you need a balanced system. Power7 enables that balance,” Starke explained in a recent news-article on TG Daily.

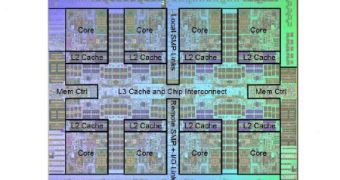

IBM's Power7 processor is said to have been designed to deliver “multiple optimization points,” including energy efficiency, upgraded thread performance, dynamic allocation of resources and an “extreme” increase in socket throughput, according to Starke. Additional details on the chip reveal that it provides support for scalability of up to 32 sockets, 32MB on chip eDRAM shared L3, dual DDR3 memory controllers, 100GB/s memory bandwidth per chip (sustained), 360GB/s SMP bandwidth/chip and 256KB L2 per core. These are the numbers behind IBM's next-generation server processor.

The performance potential of IBM's Power7 is impressive and the chip could end up faster than Intel's latest server processors, based on the chip maker's Nehalem microarchitecture. Built on a 45nm die, the new processor has been designed to accommodate multiple system configuration, including 2/4s blades and racks (single chip organic), high-end and mid-range (single chip glass ceramic) and computer intensive (Quad chip MCM).

14 DAY TRIAL //

14 DAY TRIAL //