There hasn't been a completely new major instruction set architecture since 1991, but this has finally changed now that ICube has released the UPU.

Put simply, the UPU is a chip that has both the computing and graphics instruction handled by a single processor core.

Said core bears the name of MVP (Multi-thread Virtual Pipeline) and even shares the register file.

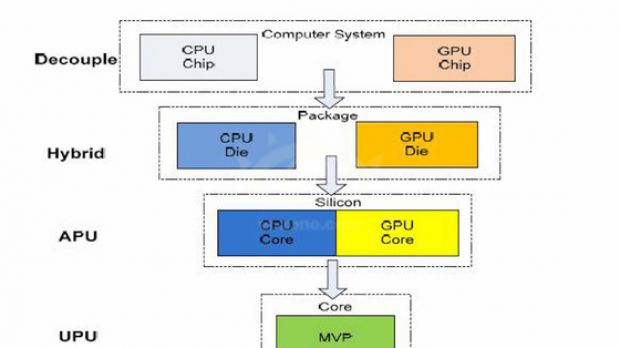

Intel, AMD and ARM have all moved towards CPUs with both computing and graphics capabilities, but the units are, in the end, still silicon dies with distinct processing and video components.

MVP offers the first truly fused CPU/GPU processor core and, since it was wholly developed in China, it has no licensing obligations or dependencies on US technology.

A UPU (Unified Processor Unit) features a 'Harmony' architecture, which has CPU and GPU threads sharing the same execution units, register file and instructions.

For comparison, an AMD APUs has different registers, execution units and instruction sets for the CPU and GPU parts.

A 32-bit RISC core, similar to the original MIPS, performs both functions, backed by a 32-unit 32-bit register file.

Parallelism is not an issue thanks to 4-way multithreading support per core (optimized logic removes the need for 4 separate register files).

The only things absent from the initial UPU version are SIMD vector (like Intel AVX) and double-precision FP (floating point).

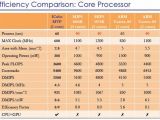

Fortunately, due to the small core footprint (2.7 square mm on 65nm, 1 square mm on 32nm) it is easy to boost performance by just adding more cores.

For perspective, up to 100 MVP cores would be crammed on an average 200 square mm CPU based on the 32nm process, along with interconnect logic and shared cache of multiple megabytes (ICube will skip one or two processing nodes, to catch up with current processors).

ICube, the company that is promoting UPU, was established by Fred Chow and Simon Moy.

Chow was chief SGI scientist, and later led development of the Pathscale compiler suite, which gave 64-bit support to AMD Opteron CPUs.

Meanwhile, Simon Moy was behind SGI's first 64-bits MIPS processors and led NVIDIA's initial GPU, Shader and GPU computing efforts (worked there for 7 years).

The first UPU, a dual-core on 65nm with single-channel DDR2-533 support, is called IC1 and works at 600 MHz.

It is aimed at affordable smartphones and tablets where Full HD media playback and 64-bit support isn't required, plus cloud servers.

64-bit with SIMD support and multi-channel DDR3 should come later.

The challenge now is that ICube has to persuade software makers to port their operating systems and make completely new BIOS, compilers, libraries, drivers and basic applications.

After that, the arduous task of persuading game and program makers to support UPU can commence.

14 DAY TRIAL //

14 DAY TRIAL //