In 2012, AMD will update its accelerated processing units lineup with a new series of chips, code named Trinity, which are built on the Bulldozer architecture and are expected to pack between 1.6 and 2 billion transistors.

This will make Trinity one of the most complex chips that AMD has built to date and its die could measure no less than 220mm2, according to estimates published by the Ozeros website.

According to the same source, the largest part of the two billion transistors will be used for the integrated graphics, which will most probably use a VLIW4 arrangement.

The rest of the chip die will be occupied by two dual-core modules, which total four processing cores, 8MB of Level 2 cache as well as by an integrated memory controller and other similar ICs.

As you can also see from the table attached, Trinity will come without any sort of Level 3 cache memory, as AMD wanted to save more space for the integrated graphics.

The resulting cores will be dubbed Piledriver and some reports indicate that Trinity will use the same AM3+ socket as the upcoming FX-series processors.

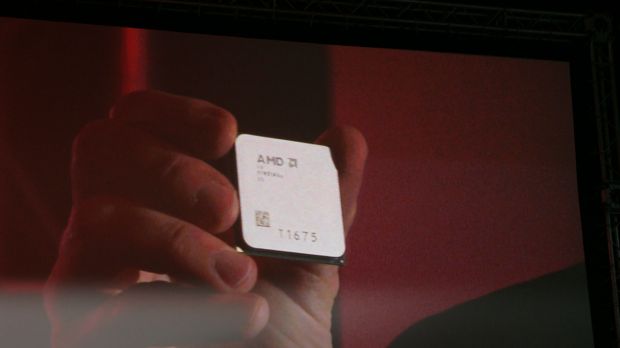

At this year's Computex fair, AMD has presented an early prototype of the Trinity APU, but it refused to comment on the development state that the chip is in.

On June 14, the Sunnyvale company will introduce its first high-performance APU design, the A-Series Llano processors, which are targeted at the high-end and mainstream notebook space as well as at the midrange desktop space.

The initial launch will include eight mobile processors that feature between two and four processing cores and have a TDP of 35 or 45 Watts, depending on the model.

Outside of the x86 CPU cores, Llano APUs also include a Radeon HD 6000-derived graphics core that packs between 160 and 400 stream processors, which work at either 400MHz or 444MHz.

14 DAY TRIAL //

14 DAY TRIAL //