During the ISSCC conference, which takes place right now in San Francisco, California, AMD has released more details about its upcoming Bulldozer processor, the Sunnyvale-based company expecting its new core to deliver 3.5GHz performance in same power and thermal envelope as AMD's prior architecture.

According to Hugh MacIntyre, a senior AMD engineer cited by the EETimes website, the core delivers linear performance across a range of frequencies and requires between 0.8V and 1.3V to operate.

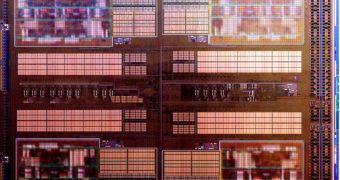

In addition, each processing module uses 213 million transistors in a 30.9mm2 block with 11 metal gates built using a 32nm SOI (silicon on insulator) process technology.

Another paper, also presented during the same conference, detailed Bulldozer's out-of-order scheduler which can store up to 40 entries as well as the chip's execution unit that is capable of issuing a maximum of four instructions per clock cycle.

Bulldozer is AMD's next-generation high-performance CPU architecture that was designed from the ground up in order to eliminate some of the redundancies that come with traditional multi-core designs.

As a result, the chip uses a modular construction, each module being comprised of two 128-bit FMA floating point units, which can be combined into one 256-bit FPU, two integer cores, with four pipelines each, and as much as 2048KB of L2 cache.

Just like the 8MB of L3 cache, the Level 2 memory will also be shared between the modules.

As Michael Golden, an AMD engineer, explained during its presentation, each dual-core module, when fully loaded, is capable of delivering 90% of the speed of a similar native dual-core processor, while featuring a lower power consumption and utilizing less die space.

This enables AMD to pack more cores inside the same die space and power budget.

Advanced Micro Devices will showcase Bulldozer at the CeBIT 2011 fair, and the official launch is expected to take place in Q2 2011.

14 DAY TRIAL //

14 DAY TRIAL //